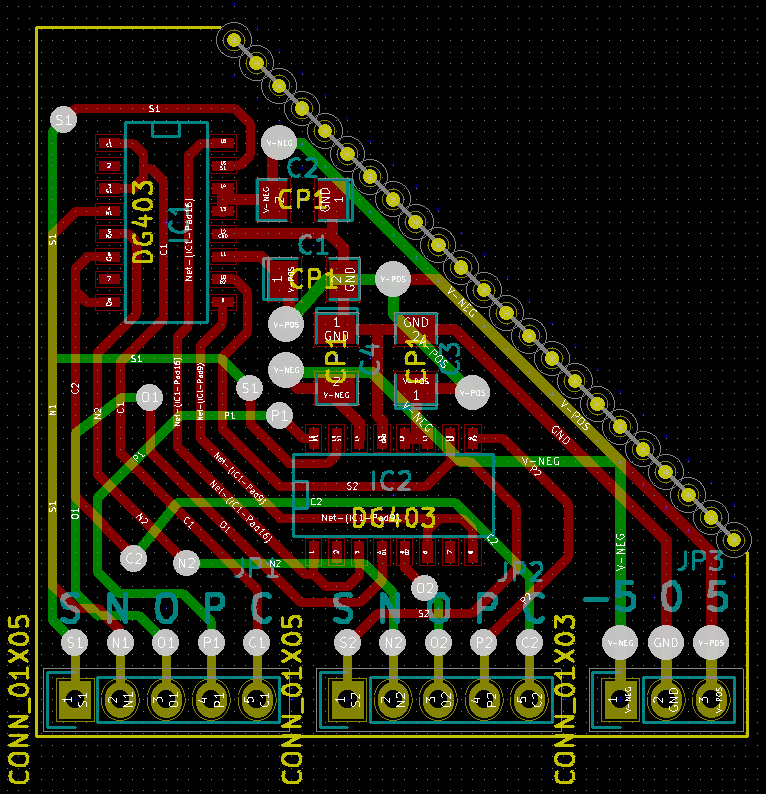

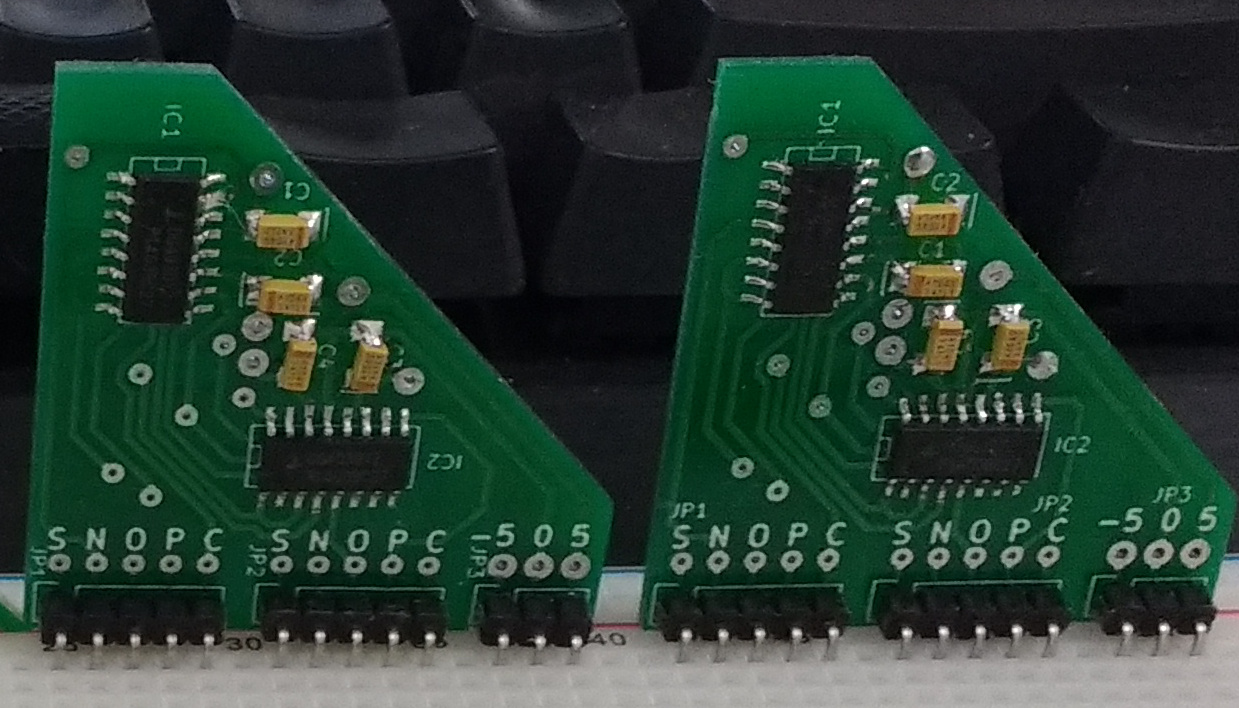

J’ai reçu les switches DG403, voici ce que ça donne une fois soudé :

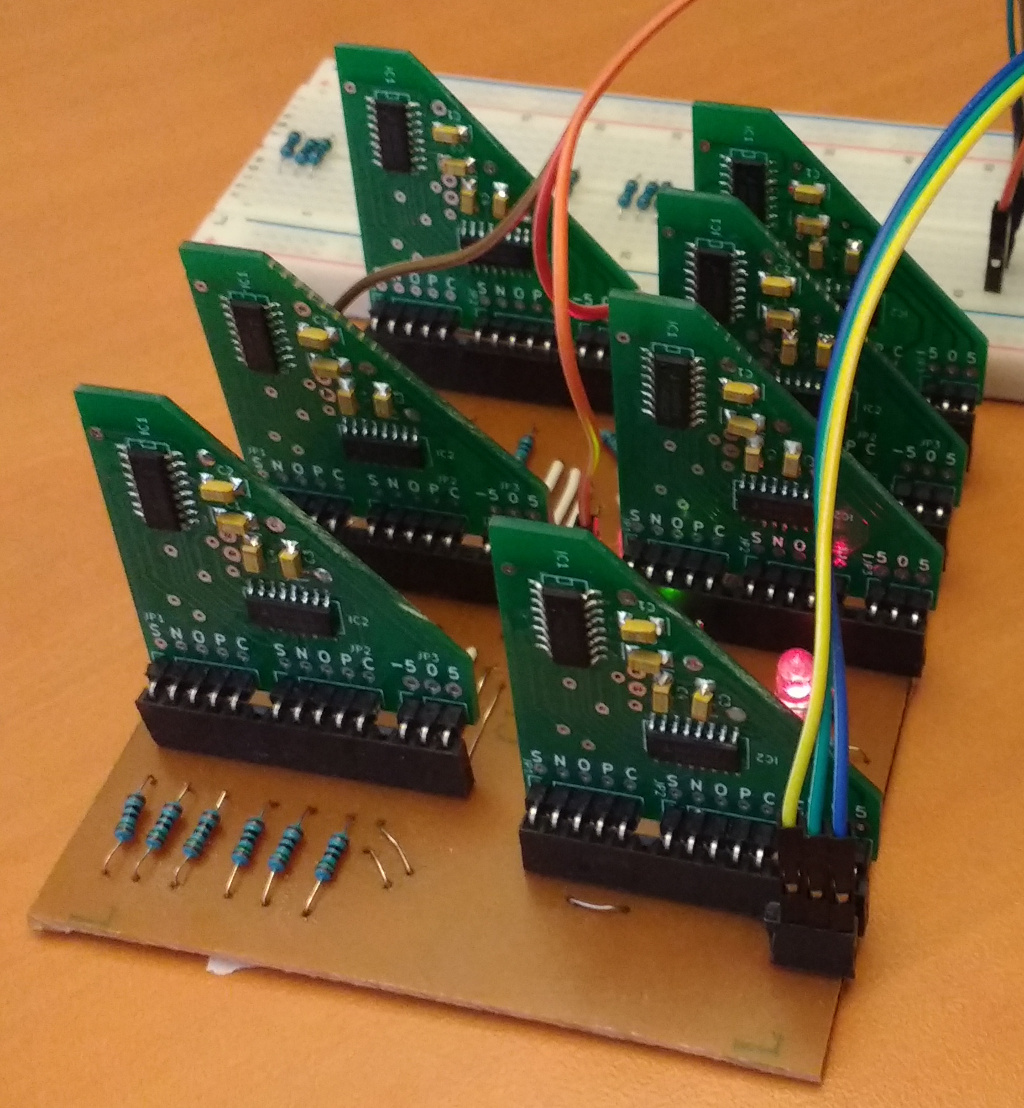

Pour le premier essai du multiplexeur ternaire je tente le demi-additionneur, il prend deux trits en entrée (A + B) et il sort le résultat (S) et le retenu (C). Les entrées et les sorties sont affichées avec des LEDs bicouleurs : rouge pour -1, éteinte pour 0 et verte pour 1. L’opération calculée est donc A + B = S + C*3.

| S,C | B | |||

| -1 | 0 | 1 | ||

| A | -1 | 1,-1 | -1,0 | 0,0 |

| 0 | -1,0 | 0,0 | 1,0 | |

| 1 | 0,0 | 1,0 | -1,1 | |

Et un petit essai avec un additionneur complet

L’additionneur complet possede trois entrées A,B et Cin, et il donne deux sorties S et Cout de sorte à ce que

A+B+Cin = S + 3*Cout.

Les trois tables suivantes donnent 27 configurations possibles. Les données sont presentées par trois tables : une pour chaque valeur de Cin. Les cellules des tables sont les couples de (S,Cout) correspondants aux entrées :

| Cin = 0 | B | |||

| -1 | 0 | 1 | ||

| A | -1 | 1,-1 | -1,0 | 0,0 |

| 0 | -1,0 | 0,0 | 1,0 | |

| 1 | 0,0 | 1,0 | -1,1 | |

| Cin = -1 | B | |||

| -1 | 0 | 1 | ||

| A | -1 | 0,-1 | 1,-1 | -1,0 |

| 0 | 1,-1 | -1,0 | 0,0 | |

| 1 | -1,0 | 0,0 | 1,0 | |

| Cin = 1 | B | |||

| -1 | 0 | 1 | ||

| A | -1 | -1,0 | 0,0 | 1,0 |

| 0 | 0,0 | 1,0 | -1,1 | |

| 1 | 1,0 | -1,1 | 0,1 | |